2023.07.16 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.05 CPU 성능 향상 기법

[혼공컴운] chapter.05 CPU 성능 향상 기법

2023.07.15 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.04 CPU의 작동원리 [혼공컴운] chapter.04 CPU의 작동원리 2023.07.06 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.03 명령어 [혼공컴운] chapter.03

zinistic.tistory.com

*기억장치 액세스 유형

1. 순차적 액세스(sequential access): 기억장치에 저장된 정보들을 처음부터 순서대로 액세스하는 방식.

2. 직접 액세스(direct acess): 읽기/쓰기 장치가 각 레코드의 근처로 직접 이동한 후 순차적 검색을 통하여 최종 위치에 도달하는 방식.

3. 임의 액세스(random access): 기억 장소들이 임의로 선택되어 액세스 되는 방식. 기억 장치 내의 어떤 위치든 액세스 시간이 동일하다.

4. 연관 액세스(associative access): 각 기억 장소에 포함된 키값의검색을 통하여 액세스할 위치를 찾아내는 방식.

06-1 RAM의 특징과 종류

- RAM의 특징

- 실행할 프로그램의 명령어와 데이터 저장

- 휘발성 저장 장치(volatile memory): 전원을 끄면 저장된 내용 사라짐.

- Random Access Memory 의 약자로 임의 액세스 방식을 이용하는 반도체 이용방식

- 데이터를 읽는 것과 쓰는 것 모두 가능. - RAM의 용량과 성능

- RAM의 용량이 작을 경우, 보조기억장치에 액세스 하는 횟수가 많아짐. 프로그램 실행 속도 저하.

- RAM의 용량이 클 경우, 보조기억장치에 액세스 하는 횟수 적어짐. 프로그램 실행 속도 상승.

=> RAM의 용량이 클수록 많은 프로그램들을 동시에 빠르게 실행하는 데 유리하다. 하지만 용량이 필요 이상으로 커졌을 때에는 속도가 그에 비례하여 증가하지 않는다.

< RAM 용량이 적은 경우 >

< RAM 용량이 충분한 경우 >

- RAM의 종류

- DRAM (Dynamic RAM): 시간이 지나면 저장된 데이터가 점차 사라지는 RAM.

- 캐패시터(축전기)에 전하를 충전하는 방식으로 비트값을 저장함. => 데이터의 저장 상태를 유지하기 위하여 주기적으로 재충전 해주어야 한다.

- 각 기억 셀이 SRAM보다 간단하고, 더 작다. => DRAM이 SRAM보다 밀도 高.

- SRAM 보다 비트 당 가격 저렴. - SRAM (Static RAM): 전력이 공급되는 동안에는 시간이 지나도 데이터가 사라지지 않는 RAM.

- 플립-플롭(flil-flop)을 이용하여 데이터를 저장하는 방식을 사용함.

- DRAM 보다 속도 빠름. - SDRAM (Synchronous Dynamic Ram): 클럭 신호와 동기화된 DRAM. 동기식 DRAM 라고도 함.

=> 주기억장치 성능 저하에 따른 병목 현상 해결을 위해 개발되었다. - DDR SDRAM (Double Data Rate SDRAM): 대역폭을 넓혀 속도를 빠르게 만든 SDRAM.

- 대역폭(bandwidth): 데이터를 주고받는 길의 너비.

- 클럭의 상승에지 뿐만 아니라 하강에지에서도 데이터가 전송됨.

( SDRAM의 경우에는 클럭의 상승에지에서만 데이터 전송 )

ex) DDR2 SDRAM 은 DDR SDRAM보다 대역폭이 두 배 넓은 SDRAM.

=> SDRAM보다 대역폭이 네 배 더 넓다.

- DRAM (Dynamic RAM): 시간이 지나면 저장된 데이터가 점차 사라지는 RAM.

★ DRAM과 SRAM의 각 특징들로 인해서 DRAM은 주기억장치 SRAM은 캐시로 사용된다. ★

* 후술할 캐시는 기억장치 계층 구조의 핵심 부품으로서 주기억장치와 CPU의 속도 차이를 보완하기 위하여 그 사이에 설치하는 반도체 기억장치이다.

06-2 메모리의 주소 공간

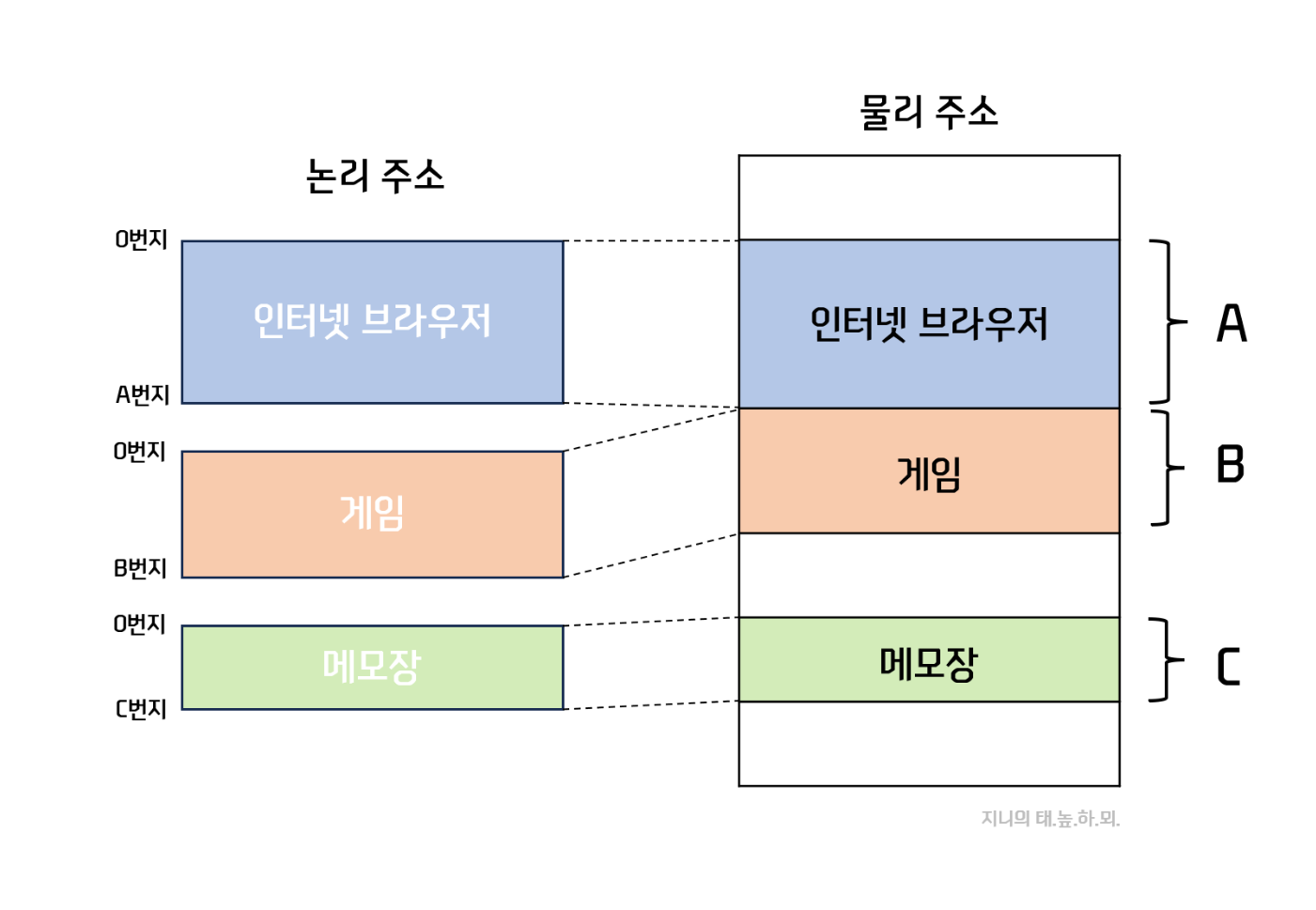

- 물리 주소와 논리 주소

- 물리 주소(physical address): 정보가 실제로 저장된 하드웨어상의 주소. 메모리가 사용하는 주소.

- 논리 주소(logical address): 실행 중인 프로그램 각각에게 부여된 0번지부터 시작되는 주소.

→ 모든 프로그램은 물리 주소가 아닌 0번지부터 시작하는 자신만을 위한 주소인 논리 주소를 가지고 있다. - MMU (Memory Management Unit, 메모리 관리 장치): 논리 주소와 물리 주소를 변환해주는 장치.

→ CPU가 발생시킨 논리 주소에 베이스 레지스터 값을 더하여 논리 주소를 물리 주소로 변환한다.

*베이스 레지스터: 프로그램의 가장 작은 물리주소. 즉, 프로그램의 첫 물리주소를 저장.

*논리 주소: 프로그램의 시작점으로부터의 거리.

< 논리 주소가 100이고 베이스 레지스터가 15000인 프로그램에 접근하는 원리 >

- 메모리 보호 기법

: 다른 프로그램의 명령어를 침범할 수 있는 명령어 실행을 방지하고 실행 중인 프로그램이 다른 프로그램에 영향을 받지 않도록 보호하는 기법.

- 한계 레지스터(limit register): 논리 주소의 최대 크기를 저장.

→ CPU가 접근하려는 논리 주소는 한계 레지스터가 저장한 값보다 크면 안됨.

→ 논리 주소가 한계 레지스터 값 보다 클 시, 접근하면 안되는 메모리 주소에 접근하게 됨.

< CPU에서 발생시킨 논리 주소를 물리 주소로 바꾸는 경우의 순서도 >

06-3 캐시 메모리

- 저장 장치 계층 구조 (memory hierarchy)

: 여러 유형의 기억장치들을 계층적으로 구성하여 설치함으로써, 평균 기억장치 액세스 속도를 높이면서 가격대성능비도 적절히 유지될 수 있게 하는 구조.

* CPU가 프로그램 코드나 데이터를 처음으로 액세스 할 때는 주기억장치로부터 직접 읽어와야 하지만, 캐시에 적재되어 있는 프로그램 코드나 데이터가 CPU에 의해 다시 사용될 때는 캐시로부터 신속히 읽어올 수 있다.

- 액세스 속도 高, 비트당 가격 高

- 용량 大, 비트당 가격 低

- 용량 大, 액세스 속도 低

<기억장치 계층>

- 캐시 메모리 (cache memory)

: CPU의 연산 속도와 메모리 접근 속도의 차이를 줄이기 위해서 탄생.

* 캐시 메모리들은 CPU와 가까운 순서대로 계층 구성.

ex) 가장 가까운 캐시 메모리는 L1 캐시.

- 분리형 캐시(split cache): 접근 속도를 조금이라도 빠르게 하기 위해서 명령어만을 저장하는 캐시와 데이터만을 저장하는 캐시를 나눈다.

< 분리형 캐시 (레벨 1에 해당하는 캐시들이 L1D(데이터), L1I(명령어)로 나뉘어 짐.)>

* 일반적으로 L1, L2 캐시는 코어 내부 L3 캐시는 코어 외부에 있다.

- 참조 지역성의 원리

*지역성(locality): CPU가 주기억장치의 특정 위치에 저장되어 있는 명령어들이나 데이터를 빈번히 액세스하는 현상.

- 시간적 지역성(temporal locality): CPU가 최근에 접근했던 메모리 공간에 다시 접근하려는 특성.

- 공간적 지역성(spatial locality): CPU가 접근한 메모리 공간 근처를 접근하려는 특성.

- 순차적 지역성(sequential locality): 분기(branch)가 발생하지 않는 한, 명령어들은 기억장치에 저장된 순서대로 인출되어 실행되는 특성. - 캐시 히트(cache hit): 캐시 메모리 내 데이터가 CPU에서 활용될 경우.

- 캐시 미스(cache miss): 캐시 메모리 내 데이터가 CPU에서 활용되지 못하고 주기억장치에서 직접 데이터를 가져와야 하는 경우.

- 캐시 적중률(cache hit ratio): 캐시 히트 횟수 / ( 캐시 히트 횟수 + 캐시 미스 횟수 )

* 캐시 미스율(cache hit ratio): ( 1 - 적중률 )

→ 캐시 적중률은 프로그램과 데이터의 지역성에 크게 의존함. - 평균 기억장치 액세스 시간: 적중률 * 캐시 액세스 시간 + ( 1 - 적중률 ) * 주기억장치 액세스 시간

*CPU는 참조 지역성의 원리에 입각해 사용할 법한 데이터를 예측한다.

* 오류 지적은 환영입니다.^^ *

'컴퓨터 공학 > 컴퓨터 구조' 카테고리의 다른 글

| [혼공컴운] chapter.08 입출력장치 (0) | 2023.07.23 |

|---|---|

| [혼공컴운] chapter.07 보조기억장치 (0) | 2023.07.23 |

| [혼공컴운] chapter.04~05 확인문제 (0) | 2023.07.16 |

| [혼공컴운] chapter.05 CPU 성능 향상 기법 (0) | 2023.07.16 |

| [혼공컴운] chapter.04 CPU의 작동원리 (0) | 2023.07.15 |