2023.07.15 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.04 CPU의 작동원리

[혼공컴운] chapter.04 CPU의 작동원리

2023.07.06 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.03 명령어 [혼공컴운] chapter.03 명령어 2023.07.06 - [컴퓨터 공학/컴퓨터 구조] - [혼공컴운] chapter.02 데이터 [혼공컴운] chapter.02 데이터 이전글

zinistic.tistory.com

05-1 빠른 CPU를 위한 설계 기법

- 클럭

- 클럭 속도: 헤르츠(Hz) 단위로 측정. 1초에 클럭이 몇 번 반복되었는지를 나타냄.

ex) 100Hz : 1초에 클럭 신호 100번 반복

* 클럭 속도는 일정하지 않을 수 있음

CPU는 최대 클럭 속도와 기본 클럭 속도를 각각 명시하여 판매하는데, 이는 CPU가 일정한 클럭 속도를 유지하지 않음을 뜻한다. 고성능을 요하는 순간에는 클럭 속도를 높이고 그렇지 않을 때는 클럭 속도를 줄이며 성능을 관리한다.

* 오버클럭킹 (overclocking)

: 최대 클럭 속도를 강제로 올리는 기법

☆ 클럭 속도를 높이는 것이 CPU를 빠르게 할 수 있으나, 클럭 속도만으로 CPU의 성능을 올리는 것은 어려움. - 코어와 멀티코어

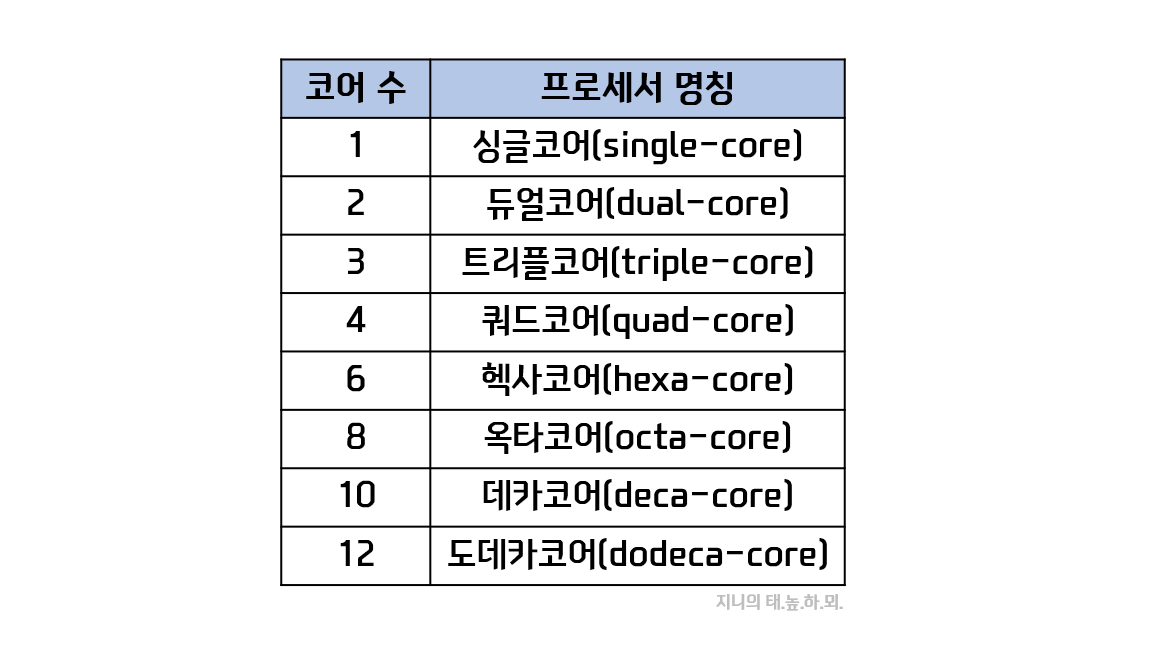

- 코어(core): 명령어를 실행하는 부품

- 멀티코어(multi-core) CPU: 코어를 여러 개 포함하고 있는 CPU. 멀티코어 프로세서 라고도 함.

- 스레드(thread)와 멀티스레드(multithread)

- 하드웨어적 스레드

: 하나의 코어가 동시에 처리하는 명령어 단위. 논리 프로세서라고도 부름.

*멀티스레드 프로세서: 하나의 코어로 여러 명령어를 동시에 처리하는 CPU. 멀티스레트 CPU라고도 함.

*하이퍼스레딩: 인텔의 멀티스레드 기술. - 소프트웨어적 스레드

: 하나의 프로그램에서 독립적으로 실행되는 단위

여러 기능을 각각의 스레드로 만들면 동시에 실행할 수 있음. - 멀티스레드 프로세서

=> 하나의 코어로 여러 명령어를 동시에 처리하도록 만듦.

* 스레드가 여러 개 라는 것은 실제로 코어로서 존재하는 것은 아니지만 명령어가 스레드의 갯수만큼 동시에 처리할 수 있는 것을 의미한다. 프로그램 입장에서 보았을 때 CPU가 스레드의 갯수 만큼 있는 것 처럼 보인다.

- 하드웨어적 스레드

05-2 명령어 병렬 처리 기법

- 명령어 파이프라인

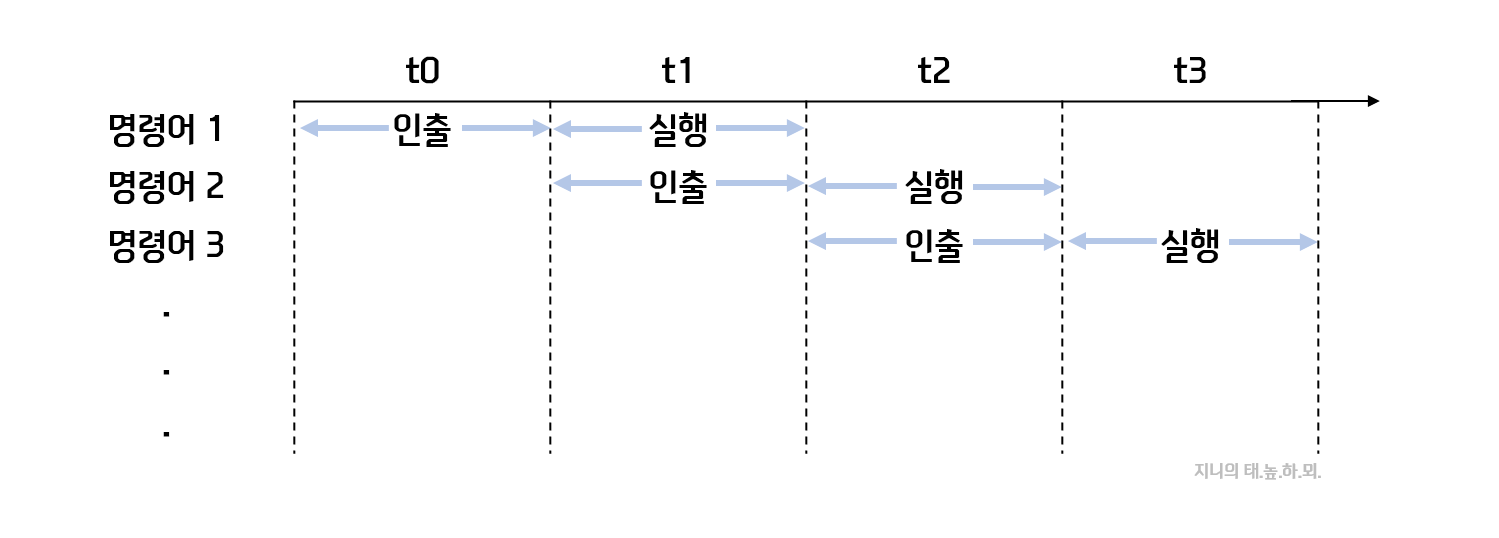

- 명령어 파이프라이닝: 명령어를 실행하는데 사용되는 하드웨어를 여러 개의 독립적인 단계로 분할하고, 동시에 서로 다른 명령어를 처리하도록 함으로써 CPU의 성능을 높여주는 기술.

<명령어 처리 과정의 예>

- 명령어 인출(Instruction Fetch)

- 명령어 해석(Instruction Decode)

- 명령어 실행(Execute Instruction)

- 결과 저장(Write Back)

* 각 단계가 겹치지 않으면 CPU는 각 단계를 동시에 실행할 수 있다. 즉 CPU는 여러 개의 명령어를 동시에 처리할 수 있다.

- 명령어 처리 과정이 2단계 일 때(2-단계 명령어 파이프라인)

=> 명령어 처리 과정을 인출 단계와 실행 단계라는 두 단계로 분리하여 구성.

(* 인출과 실행 단계는 레지스터에 접근해야 하는데 하나의 레지스터에 동시에 액세스 할 수 없다.(구조적 위험) 이 예는 모든 단계들이 동시에 수행될 수 있다는 가정하였음.)

- 명령어 처리 과정이 4단계 일 때(4-단계 명령어 파이프라인)

=> 명령어 처리 과정을 <명령어 처리 과정의 예>와 같이 분리하여 구성.

=> 한 클럭에 4개의 명령어를 동시에 실행한다. t3 부터 명령어 하나를 실행하는데 1클럭만 소요됨을 알 수 있음.

- 파이프라인 위험(pipeline hazard)

- 데이터 위험: 데이터 의존적인 두 개 이상의 명령어를 동시에 실행하려고 할 때 제대로 작동하지 않는 것.

명령어 간 데이터 의존성에 의해 발생

t0: R1 <- R2 + R3

t1: R4 <- R1 + R5=> R1에 값이 저장되기 전에 t1이 실행되면 원치 않는 값을 읽어들일 수 있다.

- 제어 위험: 조건 분기 명령어가 실행된다면 파이프라인에서 처리되고 있던 명령어들이 무효화 될 수 있는 것.

조건 분기 명령어: 조건에 따라 다른 위치로 분기하도록 하는 명령어

* 이를 해결하기 위해 분기 예측, 분기 목적지 선인출, 루프 버퍼 등 많은 기술이 개발되고 사용됨.

- 구조적 위험: 명령어들을 겹쳐 실행하는 과정에서 서로 다른 명령어가 동시에 ALU, 레지스터 등과 같은 CPU 부품을 사용하려고 할 때 발생. 자원 위험이라고도 함.

- 슈퍼스칼라(superscalar)

: CPU 내부에 여러 개의 명령어 파이프라인을 포함한 구조

슈퍼스칼라 프로세서: 슈퍼스칼라 구조로 명령어 처리가 가능한 CPU. 슈퍼스칼라 CPU 라고도 함.

- 비순차적 명령어 처리(OoOE: Out-of-order execution)

: 파이프라인의 중단을 방지하기 위해 명령어를 순차적으로 처리하지 않는 명령어 병럴 처리 기법.

=> 서로 데이터 의존성이 전혀 없어서 순서를 바꾸어 처리해도 수행 결과에 영향을 미치지 않는 명령어들을 먼저 실행하는 기법

< 비순차적 명령어 처리의 예>

1: M(100) <- 1

2: M(101) <- 2

3: M(102) <- M(100) + M(101)

4: M(150) <- 1

5: M(151) <- 2

6: M(152) <- 3=> 3번 명령어를 실행하기 위해서 1번 명령어와 2번 명령어의 실행이 끝날 때 까지 대기하여야 함.

이 코드는 다른 명령어들과 순서를 바꾸어도 문제가 없다. 데이터 의존성이 없도록 순서를 바꾸자.

1: M(100) <- 1

2: M(101) <- 2

3: M(150) <- 1

4: M(151) <- 2

5: M(152) <- 3

6: M(102) <- M(100) + M(101)

※ 아무 코드나 수정해도 되는 것은 아님을 주의!

05-3 CISC와 RISC

- 명령어 집합: CPU가 이해할 수 있는 명령어들의 모음. 명령어 집합 구조(ISA) 라고도 함.

=> 동일한 코드임에도 ISA가 다르면 CPU마다 이해하고 실행할 수 있는 명령어가 달라 어셈블리어의 형태도 다르다.

* ISA마다 장단점이 각각 다르다. 명령어 파이프라인, 슈퍼스칼라, 비순차적 명령어 처리에 유리한 ISA가 있으며, 그렇지 않은 ISA도 존재한다.

현대 ISA의 양대산맥으로 CISC와 RISC이 있다. - CISC(Complex Instruction Set Computer)

- 가변 길이 명령어 사용

- 주소 지정 방식 다양함.

- 프로그램의 명령어 수 小 => 메모리 절약

- 명령어의 크기와 수행 시간이 일정하지 않음. => 규격화되지 않은 명령어. 파이프라이닝 어려움.

=> 다양하고 복잡한 기능 지원하지만 일부 명령어만 자주 사용됨. - RISC(Reduced Instruction Set Computer)

- 고정 길이 명령어 사용

- 적은 주소 지정 방식

- 프로그램의 명령어 수 多

- 명령어의 크기와 수행시간 일정. => 파이프라이닝 쉬움.

=> 메모리 접근을 최소화 하였음. 대신 레지스터를 이용하는 연산 多

* 오류 지적은 환영입니다.^^ *

'컴퓨터 공학 > 컴퓨터 구조' 카테고리의 다른 글

| [혼공컴운] chapter.06 메모리와 캐시 메모리 (0) | 2023.07.22 |

|---|---|

| [혼공컴운] chapter.04~05 확인문제 (0) | 2023.07.16 |

| [혼공컴운] chapter.04 CPU의 작동원리 (0) | 2023.07.15 |

| [혼공컴운] chapter. 01~03 확인문제 (0) | 2023.07.08 |

| [혼공컴운] chapter.03 명령어 (0) | 2023.07.06 |